12月14日,JEDEC组织宣布启动新型内存标准SPHBM4(标准封装高带宽内存第四代)的制定工作。该标准通过512-bit位宽实现HBM4级别带宽,兼容传统有机基板,在提升容量和降低集成成本方面具有显著优势。

SPHBM4定位介于传统DDR与HBM内存之间,主要面向AI加速、高性能计算等领域。与采用1024-bit或2048-bit位宽的HBM内存相比,其512-bit位宽设计大幅减少了芯片面积占用,有助于提升单颗堆叠数量和封装容量。

技术层面,SPHBM4采用4:1串行技术,将位宽从2048-bit压缩至512-bit,同时保持同等带宽水平。JEDEC尚未明确该技术是通过提升数据传输率至32GT/s,还是采用新型编码方案实现这一目标。

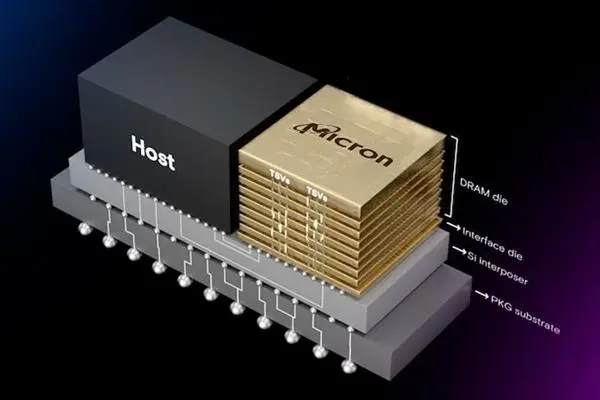

在封装设计上,SPHBM4沿用标准基础Die和HBM4 Die,确保单堆叠容量与HBM4/HBM4E保持一致,最高可达64GB。这种设计简化了控制器结构和整体封装方案,有效降低了生产成本。

值得注意的是,SPHBM4虽然具备HBM4级带宽优势,但不会应用于显卡领域取代GDDR显存。其设计重点在于性能与容量优化,而非成本和功耗控制,这使得其价格定位仍高于普通DRAM芯片。

与HBM4相比,SPHBM4因无需使用昂贵中介层而具备成本优势,但仍需配套基片接口、TSV硅通孔等先进封装技术。在显卡应用场景中,单颗SPHBM4的成本将显著高于多颗GDDR6/7组合,且性能提升效果有限。

市场分析认为,SPHBM4主要填补HBM内存在大规模计算领域的应用空白。其技术特点更适合AI训练、数据中心等对带宽和容量要求较高的场景,而非消费级图形处理需求。

行业专家指出,SPHBM4的推出标志着内存技术向更高效能方向发展。该标准有望在2025年完成制定,届时将为高性能计算领域提供更具成本效益的内存解决方案。

阅读前请先查看【免责声明】本文内容仅用于信息整理与交流参考,相关信息来源于互联网公开渠道或已公开资料的整理与编辑。文中涉及的观点、数据及相关内容,仅代表作者个人或整理立场,不代表本站观点.如本文内容涉及版权或其他合法权益问题,请相关权利人及时与本站联系,本站将在核实后依法依规进行处理。 转载请注明出处:https://www.luodizhixing.com/news/276.html